# **NEX83288**

# Transition mode boost Power Factor Correction controller Rev. 1.1 — 16 September 2025 Product data sheet

## 1. General description

NEX83288 is a Power Factor Correction (PFC) controller. It supports transition mode (CrM/DCM) operations.

The device uses average current mode based VOT-control to achieve high power factor and low-current total harmonic distortion (THD) over a wide line voltage. The device features a very low supply current in burst mode. This allows the device to achieve low standby power loss.

The switching frequency near the line voltage zero cross region is reduced by the control method. It improves efficiency.

NEX83288 features overvoltage protection (OVP), cycle-by-cycle (CBC) current limit, open-loop protection (OLP), overtemperature protection (OTP), brown-in and brown-out.

NEX83288 is available in SO8 package.

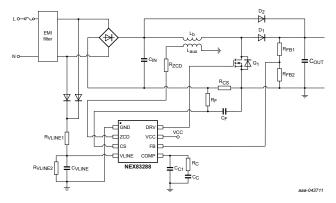

Fig. 1. Typical application

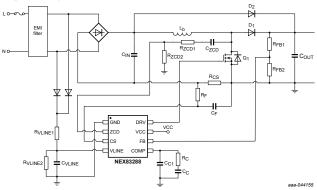

Fig. 2. Typical application without auxiliary winding

### 2. Features and benefits

- Adaptive variable on time control

- Transition mode (CrM/DCM) operations

- · Supports E-mode GaN HEMT direct drive

- · Line voltage feed forward

- · Integrated THD enhancement circuit

- · Integrated dynamic enhancement circuit

- Maximum switching frequency clamp to reduce the losses

- Valley/zero-voltage switching for minimum switching losses

- Rich protections:

- VCC UVLO/OVP

- Output OVP

- · Cycle-by-cycle (CBC) current limit

- Open-loop protection (OLP)

- Overtemperature protection (OTP)

- · Brown-in/brown-out

- Available in SO8 package

## 3. Applications

- · Monitors or LCD televisions

- Personal computer power adapters

- USB Power Delivery quick chargers

- All off-line appliances requiring power factor correction

#### **Table 1. Device information**

| Part number | Package | Body size                 |

|-------------|---------|---------------------------|

| NEX83288    | SO8     | 4.9 mm x 3.9 mm x 1.75 mm |

#### **Transition mode boost Power Factor Correction controller**

# 4. Ordering information

#### **Table 2. Ordering information**

| Type number | Temperature range (T <sub>j</sub> ) |     |                                                                                        | Version |

|-------------|-------------------------------------|-----|----------------------------------------------------------------------------------------|---------|

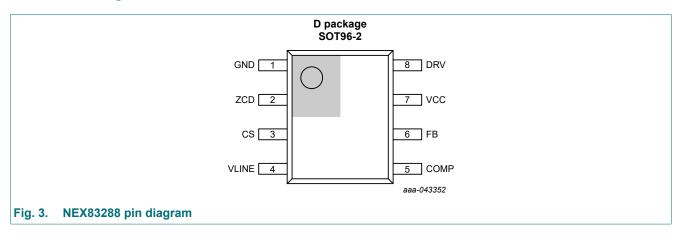

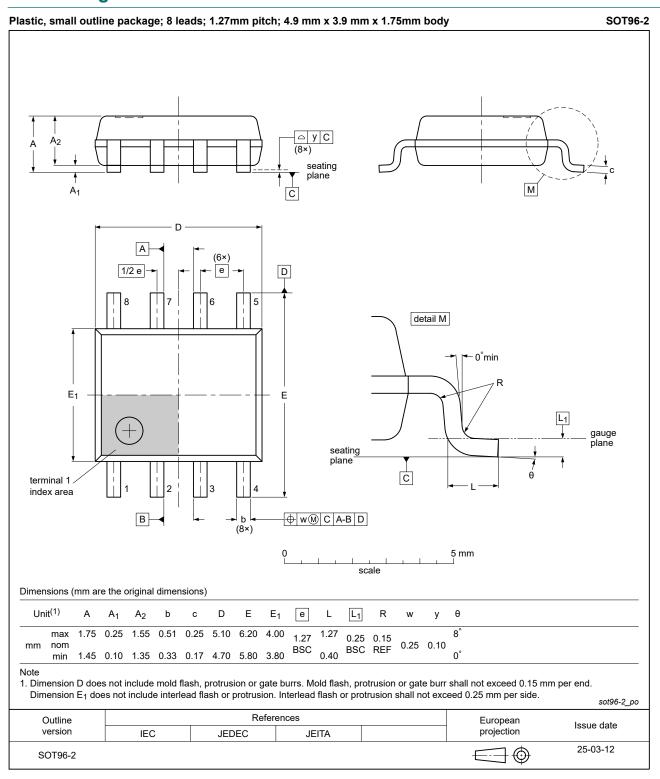

| NEX83288D   | -40 °C to 150 °C                    | SO8 | plastic, small outline package; 8 leads; 1.27 mm pitch; 4.9 mm x 3.9 mm x 1.75 mm body | SOT96-2 |

# 5. Marking

#### Table 3. Marking code

| Type number | Marking code |

|-------------|--------------|

| NEX83288D   | N83288       |

# 6. Pin configuration and description

# 6.1. Pin configuration

# 6.2. Pin description

| Symbol | Pin | I/O | Description                                                                              |

|--------|-----|-----|------------------------------------------------------------------------------------------|

| GND    | 1   | PWR | GND supply pin                                                                           |

| ZCD    | 2   | IN  | input from auxiliary winding for demagnetization timing and valley detection for PFC     |

| CS     | 3   | IN  | current sense input for PFC                                                              |

| VLINE  | 4   | IN  | sense input for line voltage                                                             |

| СОМР   | 5   | OUT | loop compensation pin;<br>the compensation network is connected between this pin and GND |

| FB     | 6   | IN  | output voltage sense pin                                                                 |

| VCC    | 7   | PWR | supply voltage                                                                           |

| DRV    | 8   | OUT | gate driver output pin                                                                   |

2/32

#### **Transition mode boost Power Factor Correction controller**

# 7. Limiting values

#### **Table 4. Limiting values**

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).[1]

| Symbol           | Parameter            | Conditions      | Min  | Max | Unit |

|------------------|----------------------|-----------------|------|-----|------|

| VCC              | supply voltage       |                 | -0.3 | 40  | V    |

| $V_{ZCD}$        | -                    | current limited | -0.3 | 6.5 | V    |

| V <sub>CS</sub>  |                      | current limited | -1   | 5.5 | V    |

| $V_{VLINE}$      | pin voltage          | current limited | -0.3 | 5.5 | V    |

| $V_{COMP}$       | - piii voitage       | current limited | -0.3 | 5.5 | V    |

| $V_{FB}$         |                      | current limited | -0.3 | 5.5 | V    |

| $V_{DRV}$        |                      | current limited | -0.3 | 13  | V    |

| Tj               | junction temperature |                 | -40  | 150 | °C   |

| T <sub>stg</sub> | storage temperature  |                 | -65  | 150 | °C   |

<sup>[1]</sup> Stresses beyond those conditions under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 8. ESD ratings

#### Table 5. ESD ratings

| Symbol            | Parameter                             | Conditions                          | Min   | Тур | Max  | Unit |

|-------------------|---------------------------------------|-------------------------------------|-------|-----|------|------|

| V                 | electrostatic                         | HBM: ANSI/ESDA/JEDEC JS-001 class 2 | -2000 | -   | 2000 | V    |

| discharge voltage | CDM: ANSI/ESDA/JEDEC JS-002 class C2a | -500                                | -     | 500 | V    |      |

# 9. Recommended operating conditions

### Table 6. Recommended operating conditions

| Symbol             | Parameter            | Conditions | Min | Max | Unit |

|--------------------|----------------------|------------|-----|-----|------|

| VCC                | supply voltage       |            | 14  | 33  | V    |

| V <sub>VLINE</sub> | sensed line voltage  |            | 0   | 5   | ٧    |

| Tj                 | junction temperature |            | -40 | 125 | °C   |

### 10. Thermal characteristics

#### Table 7. Thermal characteristics

| Symbol                | Parameter                                 | SOT96-2 (SO8) | Unit |

|-----------------------|-------------------------------------------|---------------|------|

| $R_{\Theta JA}$       | junction-to-ambient thermal resistance    | 160           | °C/W |

| R <sub>OJC(top)</sub> | junction-to-case (top) thermal resistance | 85            | °C/W |

| $R_{\Theta Jb}$       | junction-to-board thermal resistance      | 125           | °C/W |

| ФЈТ                   | junction to top char parameter            | 39            | °C/W |

#### **Transition mode boost Power Factor Correction controller**

# 11. Electrical characteristics

#### **Table 8. Electrical characteristics**

Where VCC = 18 V; typical values are measured  $T_i$  = 25 °C (unless otherwise noted).

| 0                        | D                                                        | O a malifica ma                                               |      | T <sub>j</sub> = -40 °C to 125 °C |       |      |

|--------------------------|----------------------------------------------------------|---------------------------------------------------------------|------|-----------------------------------|-------|------|

| Symbol                   | Parameter                                                | Conditions                                                    | Min  | Тур                               | Max   | Unit |

| Supply (VCC              | pin)                                                     |                                                               |      |                                   |       |      |

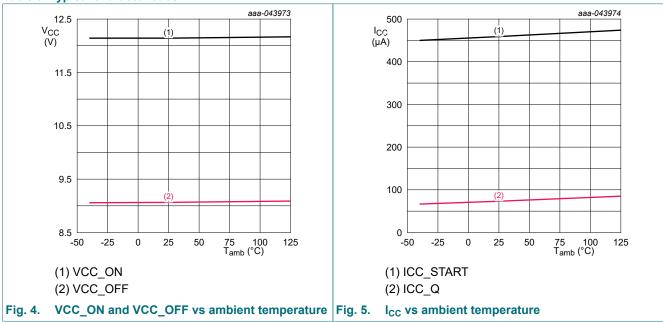

| V <sub>VCC_ON</sub>      | VCC on threshold voltage                                 | VCC rising                                                    | 11.4 | 12                                | 12.8  | V    |

| V <sub>VCC_OFF</sub>     | VCC off threshold voltage                                | VCC falling                                                   | 8.5  | 9                                 | 9.5   | V    |

| V <sub>VCC_OVP_H</sub>   | over voltage protection voltage high threshold           | VCC rising                                                    | 33.5 | 36                                | 39.3  | V    |

| V <sub>VCC_OVP_L</sub>   | over voltage protection voltage low threshold            | VCC falling                                                   | 31   | 34                                | 37.5  | V    |

| I <sub>VCC_STARTUP</sub> | operating current<br>during normal<br>operation          | VCC = 9.5 V during start-up                                   | -    | -                                 | 120   | μА   |

| I <sub>VCC_Q</sub>       | operating quiescent current                              | DRV pin is floating, or device is non-switching               | -    | 0.45                              | 0.63  | mA   |

|                          |                                                          | f <sub>SW</sub> = 89 kHz; C <sub>Load</sub> = 1 nF on DRV pin | -    | 1.5                               | 3.8   | mA   |

| I <sub>VCC_NOM</sub>     | VCC normal operating current                             | $f_{SW}$ = 135 kHz; $C_{Load}$ = 1 nF on DRV pin              | -    | 4.6                               | 6.2   | mA   |

|                          | Garroni                                                  | $f_{SW}$ = 260 kHz; $C_{Load}$ = 1 nF on DRV pin              | -    | 5                                 | 7.5   | mA   |

| Gate driver or           | utput (DRV pin)                                          |                                                               |      | ,                                 |       |      |

| I <sub>DRV_SOURCE</sub>  | DRV source current capability                            | V <sub>DRV</sub> = 2 V; V <sub>VCC</sub> ≥ 12 V               | -    | -0.6                              | -     | А    |

| I <sub>DRV_SINK</sub>    | DRV sink current capability                              | V <sub>DRV</sub> = 10 V; V <sub>VCC</sub> ≥ 12 V              | -    | 1.4                               | -     | А    |

| V <sub>DRV_MAX</sub>     | maximum DRV voltage<br>for MOSFET and D-<br>mode GaN FET |                                                               | 11.1 | 12                                | 13    | V    |

| _                        | maximum DRV voltage for E-mode GaN FET                   |                                                               | 5.56 | 6.08                              | 6.78  | V    |

|                          | voltage rising time for MOSFET                           | C <sub>Load</sub> = 1 nF; 10% to 90% of output signal         | -    | 63                                | -     | ns   |

| t <sub>R</sub>           | voltage rising time for GaN FET                          | C <sub>Load</sub> = 150 pF; 10% to 90% of output signal       | -    | 56                                | -     | ns   |

| <b>t</b> _               | voltage falling time for MOSFET                          | C <sub>Load</sub> = 1 nF; 10% to 90% of output signal         | -    | 16.5                              | -     | ns   |

| t <sub>F</sub>           | voltage falling time for GaN FET                         | C <sub>Load</sub> = 150 pF; 10% to 90% of output signal       | -    | 2.3                               | -     | ns   |

| f <sub>sw_max</sub>      | maximum switching frequency                              | middle frequency version                                      | 115  | 135                               | 155   | kHz  |

| Zero-current             | detection (ZCD pin)                                      |                                                               |      |                                   |       |      |

| .,                       | zero-current detection                                   | MOSFET                                                        | 1.9  | 2.1                               | 2.3   | V    |

| V <sub>ZCD_DETA</sub>    | arming threshold voltage on ZCD pin                      | GaNFET                                                        | 1.34 | 1.4                               | 1.43  | V    |

|                          | zero-current detection                                   | MOSFET                                                        | 1.44 | 1.4                               | 1.76  | V    |

| V <sub>ZCD_DETT</sub>    | trigger threshold voltage on ZCD pin                     | GaNFET                                                        | 0.64 | 0.7                               | 0.755 | V    |

### **Transition mode boost Power Factor Correction controller**

| Symbol                    | Parameter                                                    | Conditions                                   |       | T <sub>j</sub> = -40 °C to 125 °C |       |      |

|---------------------------|--------------------------------------------------------------|----------------------------------------------|-------|-----------------------------------|-------|------|

| Symbol                    | Parameter                                                    | Conditions                                   | Min   | Тур                               | Max   | Unit |

| I <sub>ZCD_DET</sub>      | protection current for ZCD                                   |                                              | 5     | -                                 | -     | mA   |

| t <sub>TIME_OUT</sub>     | zero-current detection arming time-out time                  |                                              | -     | 30                                | -     | μs   |

| V <sub>ZCD_CLAMP_</sub> H | upper voltage clamp on ZCD pin                               |                                              | 5.13  | 5.70                              | 6.27  | V    |

| V                         | lower voltage clamp on                                       | MOSFET                                       | 5.35  | 5.8                               | 6.55  | V    |

| V <sub>ZCD_CLAMP_L</sub>  | ZCD pin                                                      | GaNFET                                       | 0     | 0.32                              | 0.55  | V    |

| <b>.</b>                  | turn-on delay after ZCD                                      | MOSFET                                       | -     | 100                               | -     | ns   |

| ZCD_DELAY                 | detected                                                     | GaNFET                                       | -     | 50                                | -     | ns   |

| Current sensir            | ng (CS pin)                                                  |                                              |       |                                   |       | •    |

| V <sub>CBC_OCP</sub>      | inductor saturation protection threshold                     | enable CBC function                          | -0.55 | -0.49                             | -0.44 | V    |

| Line voltage d            | etection (VLINE pin)                                         |                                              | '     |                                   |       |      |

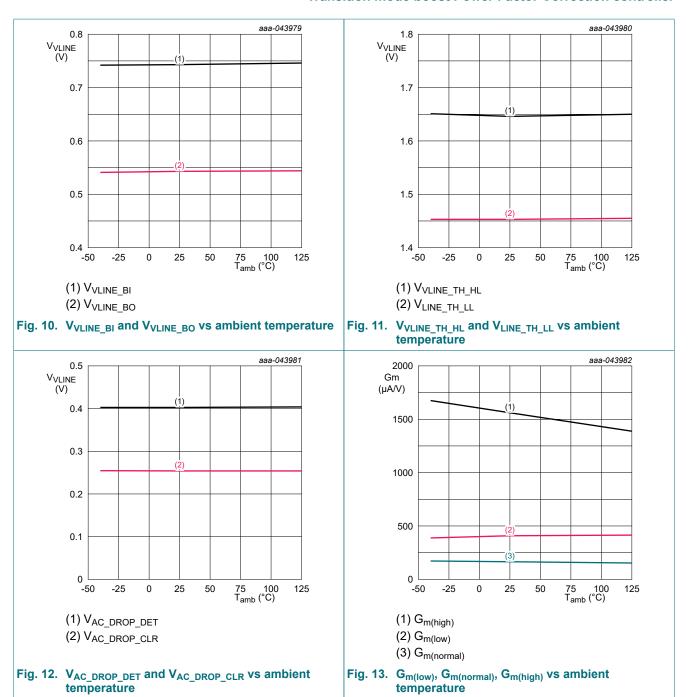

| V <sub>LINE_BI</sub>      | brown-in voltage<br>threshold                                |                                              | 0.698 | 0.750                             | 0.802 | V    |

| V <sub>LINE_BO</sub>      | brown-out voltage<br>threshold                               |                                              | 0.500 | 0.550                             | 0.600 | V    |

| V <sub>BO(HYS)</sub>      | brown-out comparator hysteresis                              |                                              | -     | 0.2                               | -     | V    |

| V <sub>LINE_TH_HL</sub>   | high line detection threshold                                |                                              | 1.57  | 1.65                              | 1.73  | V    |

| V <sub>LINE_TH_LL</sub>   | low line detection threshold                                 |                                              | 1.38  | 1.45                              | 1.52  | V    |

| t <sub>LINE_DET_DB</sub>  | the debounce time from<br>high line to low line<br>detection |                                              | -     | 50                                | -     | ms   |

| V                         | AC drop start detection threshold                            |                                              | 0.20  | 0.25                              | 0.30  | V    |

| V <sub>LINE_AC_DROP</sub> | AC drop stop detection threshold                             |                                              | 0.34  | 0.4                               | 0.45  | V    |

| t <sub>AC_DROP</sub>      | AC drop detection time                                       |                                              | -     | 5                                 | -     | ms   |

| t <sub>BO_DB</sub>        | brown-out detection debounce time                            |                                              | -     | 50                                | -     | ms   |

| Regulation and            | d compensation (COMP                                         | pin)                                         |       |                                   |       |      |

| $V_{REF}$                 | output reference voltage                                     |                                              | 2.463 | 2.500                             | 2.550 | V    |

| G <sub>m(low)</sub>       |                                                              | V <sub>FB</sub> = 2.25 V to 2.35 V           | 100   | 400                               | 750   | μΑ/V |

| G <sub>m(normal)</sub>    | transconductance                                             | V <sub>FB</sub> = 2.45 V to 2.55 V           | 132   | 160                               | 185   | μΑ/V |

| G <sub>m(high)</sub>      |                                                              | V <sub>FB</sub> = 2.6 V to 2.7 V             | 1050  | 1500                              | 1870  | μΑ/V |

|                           |                                                              | V <sub>FB</sub> < 2.1 V at normal operation  | 70    | 125                               | 180   | μΑ   |

|                           |                                                              | V <sub>FB</sub> = 2.45 V at normal operation | 1     | 8                                 | 16    | μA   |

| I <sub>COMP_source</sub>  | source current on COMP pin                                   | TM version during startup                    | 18    | 30                                | 42    | μΑ   |

|                           | John Pill                                                    | MM version at high line during startup       | 36    | 57                                | 78    | μΑ   |

|                           |                                                              | MM version at low line during startup        | 12    | 24                                | 42    | μA   |

| I                         | sink current on COMP                                         | V <sub>FB</sub> = 2.55 V                     | -12.5 | -8.6                              | -4.75 | μΑ   |

| I <sub>COMP_sink</sub>    | pin                                                          | V <sub>FB</sub> = 2.65 V                     | -143  | -98                               | -55   | μΑ   |

#### **Transition mode boost Power Factor Correction controller**

| Symbol                   | Parameter                             | Conditions                                                         | $T_j = -4$ | Unit  |       |       |

|--------------------------|---------------------------------------|--------------------------------------------------------------------|------------|-------|-------|-------|

|                          |                                       | Conditions                                                         | Min        | Тур   | Max   | Ullit |

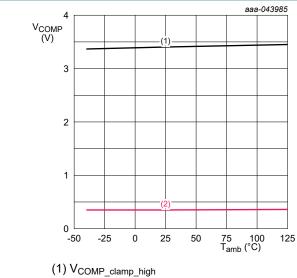

| V.                       | clamp voltage on                      | upper clamp voltage; unidirectional clamp; operating mode; PFC on; | 3.1        | 3.5   | 3.9   | V     |

| $ m V_{COMP\_clamp}$     | COMP pin                              | lower clamp voltage; unidirectional clamp; operating mode; PFC on; | 0.29       | 0.35  | 0.41  | V     |

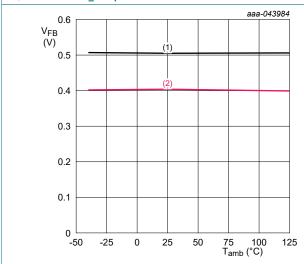

| V <sub>BURST_TH</sub>    | burst mode voltage threshold          |                                                                    | 0.470      | 0.500 | 0.535 | V     |

| Output voltag            | e sensing (FB pin)                    |                                                                    |            |       | '     | '     |

| V <sub>FB_OLP_H</sub>    | open-loop protection                  |                                                                    | 0.42       | 0.50  | 0.58  | V     |

| V <sub>FB_OLP_L</sub>    | threshold                             |                                                                    | 0.34       | 0.40  | 0.47  | V     |

| t <sub>OLP_R</sub>       | OLP recovery time                     |                                                                    | -          | 219   | -     | ms    |

| t <sub>OLP_DB</sub>      | open-loop protection debounce time    |                                                                    | -          | 50    | -     | μs    |

| t <sub>DELAY_START</sub> | start-up delay time                   | after open-loop protection removed                                 | -          | 5     | -     | ms    |

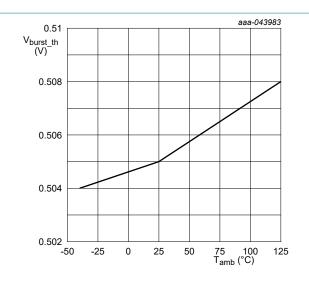

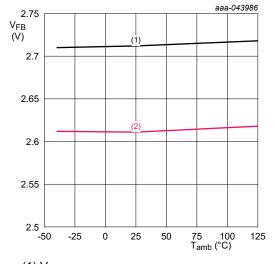

| V <sub>FB_OVP_H</sub>    | overvoltage protection                |                                                                    | 2.64       | 2.70  | 2.77  | V     |

| V <sub>FB_OVP_L</sub>    | threshold                             |                                                                    | 2.5        | 2.6   | 2.7   | V     |

| t <sub>OVP_DB</sub>      | overvoltage protection debounce time  |                                                                    | -          | 20    | -     | μs    |

| I <sub>FB_FOLLOW</sub>   | FB source current for following boost |                                                                    | 18         | 20    | 22    | μA    |

| t <sub>transition</sub>  | following boost<br>transition time    |                                                                    | -          | 30    | -     | ms    |

| Overtemperat             | ure protection (internal              | OTP)                                                               |            |       |       |       |

| T <sub>OTP</sub>         | OTP trigger level                     |                                                                    | -          | 150   | -     | °C    |

| T <sub>OTP_HYS</sub>     | OTP hysteresis                        |                                                                    | -          | 50    | -     | °C    |

# 12. Typical characteristics

**Table 9. Typical characteristics**

#### **Transition mode boost Power Factor Correction controller**

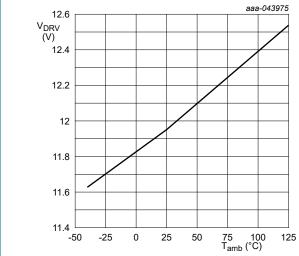

Fig. 6.

75 100 T<sub>amb</sub> (°C)

125

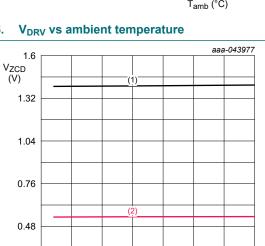

(1) V<sub>ZCD\_DETA</sub> (2) V<sub>ZCD\_DETT</sub>

-25

0.2

-50

$V_{\text{ZCD\_DETA}}$  and  $V_{\text{ZCD\_DETT}}$  vs ambient Fig. 8. temperature

0

25

50

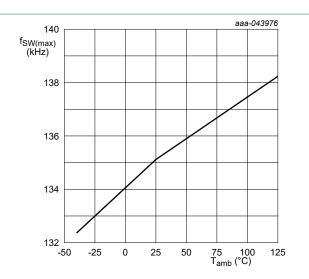

Fig. 7.  $f_{SW\_max}$  vs ambient temperature

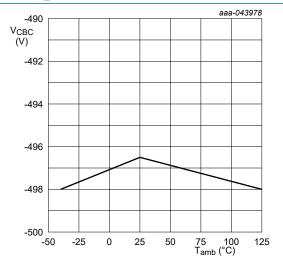

Fig. 9. V<sub>CBC\_OCP</sub> vs ambient temperature

#### **Transition mode boost Power Factor Correction controller**

temperature

#### **Transition mode boost Power Factor Correction controller**

- - (2)  $V_{COMP\_clamp\_low}$

Fig. 14. V<sub>COMP\_clamp</sub> vs ambient temperature

- (1) V<sub>FB OLP H</sub>

- (2)  $V_{FB\_OLP\_L}$

Fig. 16. V<sub>FB\_OLP\_H</sub> and V<sub>FB\_OLP\_L</sub> vs ambient temperature

Fig. 15. V<sub>BURST\_TH</sub> vs ambient temperature

- (1) V<sub>FB OVP H</sub>

- (2)  $V_{FB\_OVP\_L}$

Fig. 17.  $V_{FB\_OVP\_H}$  and  $V_{FB\_OVP\_L}$  vs ambient temperature

#### **Transition mode boost Power Factor Correction controller**

## 13. Detailed Description

#### 13.1. Overview

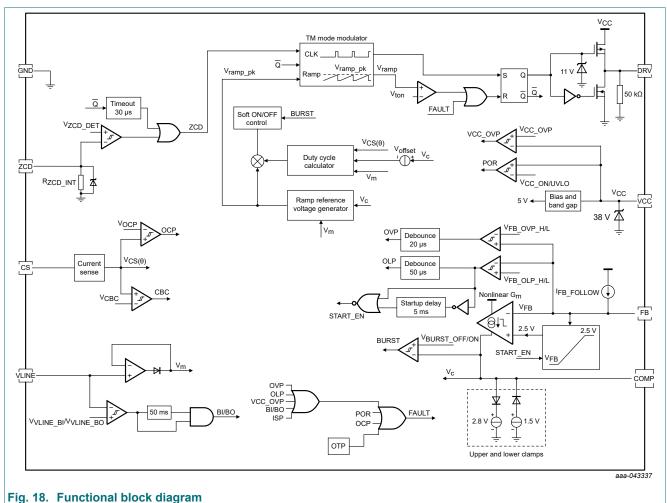

NEX83288 is a boost power factor correction (PFC) controller, which supports transition mode (TM) operation. Using the average current mode (ACM) based on time control technology, the device implements adaptive variable on time (VOT) control to achieve a high PF.

The device supports both MOSFET/D-mode GaN FET and E-mode GaN FET direct drive option. The maximum frequency can reach 135 kHz and 260 kHz respectively for MOSFET and E-mode GaN FET. In addition, it supports 2-level following boost function option.

The device supports line voltage feed forward and integrates a nonlinear transconductance error amplifier circuit to improve the large-scale dynamic response. It also integrates THD enhancement circuit to improve the current distortion.

### 13.2. Functional block diagram

Fig. 18 shows the functional block diagram of NEX83288:

rig. 16. Fullctional block diagram

#### **Transition mode boost Power Factor Correction controller**

### 13.3. Feature description

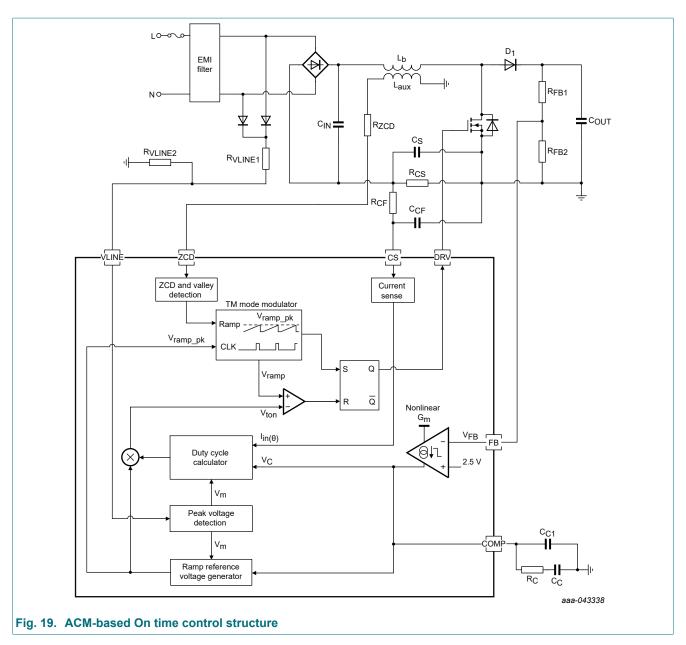

#### 13.3.1. ACM-based On time control

NEX83288 adopts a unified average current mode based on time control technology. Based on Volt-Second balance, the On time is given by equation (1).

$$t_{on}(\theta) = \left[1 - \frac{v_{in}(\theta)}{v_o}\right] T_s \tag{1}$$

Since the PFC converter can adjust the power factor to 1, the input impedance for PFC converter is

$$R_{in\_eq} = \frac{v_{in}(\theta)}{i_{in}(\theta)} \tag{2}$$

According to equation (2), the input current is always tracking the input voltage as long as  $R_{in\_eq}$  is constant. Combine equation (1) and (2), and the On time is given by

$$t_{on}(\theta) = \left[1 - \frac{R_{in\_eq}i_{in}(\theta)}{v_o}\right]T_s \tag{3}$$

According to equation (3), the On time is related to the input current (inductor current average value). When  $R_{in\_eq}$  is constant, the input current is always tracking the input voltage. If  $\frac{R_{in\_eq}}{v_o}$  is generated by the control loop and  $i_{in}(\Theta)$  is the actual input current, the input current will automatically track the input voltage. According to the above analysis, the input current will auto-track the line voltage and achieve a high power factor. For CrM/DCM mode, the actual switching frequency  $f_{s\_act}$  will be smaller than  $1/t_{s}$ .

Fig. 19 shows the control structure of ACM-based On time control method.

#### **Transition mode boost Power Factor Correction controller**

According to equation (3) and Fig. 19, based on the ACM control, the On time is given by

$$V_{t_{on}}(\theta) = \left[1 - \frac{k_r^2 V_m^2 k V_{L\_av}(\theta)}{V_C}\right] V_{ramp\_pk}$$

(4)

Where k is the gain of the analog multiplier,  $k_r$  is the division resistor ratio for line voltage peak value detection,  $V_m$  is the line voltage peak value. The control loop generates  $V_c$ , which can be seen as  $\frac{kv_ok_r^2V_m^2R_{cs}}{R_{in\_eq}}$ , the On time is calculated by the actual input current which will track the input voltage. For TM mode, the equation of ramp signal peak value is given by

$$V_{ramp\_pk} = V_{ramp\_pk\_ref} + k_{f\_TM} V_c - k_{l\_TM} k_r V_m$$

(5)

Where  $V_{ramp\_pk\_ref}$  is 1,  $k_{f\_TM}$  is 0.75, and  $k_{l\_TM}$  is 1. Substitute equation (5) into (4), and the On time is given by

$$V_{t_{on}}(\theta) = \left[1 - \frac{k_r^2 V_m^2 k_V L_a v(\theta)}{V_c}\right] \left(V_{ramp\_pk\_ref} + k_{f\_TM} V_c - k_{l\_TM} k_r V_m\right)$$

(6)

According to equation (6), the peak current is given by

NEX83288

All information provided in this document is subject to legal disclaimers

© Nexperia B.V. 2025. All rights reserved

#### **Transition mode boost Power Factor Correction controller**

$$i_{pk}(\theta) = \frac{V_{in}(\theta)C_{ch}}{I_{ch}L_b} \left[ 1 - \frac{k_r^2 V_m^2 k V_{L_av}(\theta)}{V_c} \right] \left( V_{ramp\_pk\_ref} + k_{f\_TM} V_c - k_{l\_TM} k_r V_m \right)$$

$$(7)$$

Where  $C_{ch}$  is the internal capacitor,  $I_{ch}$  is the internal charge current,  $L_b$  is the boost inductor. When the PFC controller is operating in CrM, the input current in half line cycle ([0,  $\pi$ ]) is given by

$$i_{in}(\theta) = \frac{V_{in}(\theta)C_{ch}}{2I_{ch}L_b} \left[ 1 - \frac{k_r^2 V_m^2 k V_{cs}(\theta)}{V_c} \right] \left( V_{ramp\_pk\_ref} + k_{f\_TM} V_c - k_{l\_TM} k_r V_m \right)$$

(8)

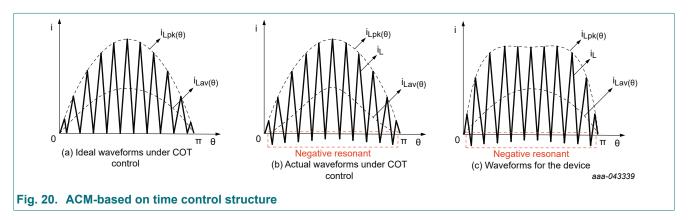

Fig. 20 (a) shows the ideal waveforms under COT control. However, with consideration of the valley switching, the actual waveforms under COT control are shown in Fig. 20 (b).

The inductor current has negative resonant stage which reduces the input current average value and causes severe current distortion. Equation (8) is an ideal theoretical formula without considering the negative resonant. Based on equation (7), the inductor current peak value is not sinusoidal as shown in Fig. 20 (c).

In addition, the input current is approximately regulated to be sinusoidal with consideration of the negative resonant.

The recommended inductor value and current sense resistor for NEX83288 under different load conditions are shown in Table 10.

Table 10. Recommended inductor value and current sense resistor

| Maximum output power (W) | Inductor value (µH) | Current sense resistor (mΩ) |

|--------------------------|---------------------|-----------------------------|

| 160                      | 200                 | 75                          |

| 200                      | 170                 | 50                          |

| 240                      | 130                 | 50                          |

| 300                      | 110                 | 30                          |

#### 13.3.2. Loop compensation

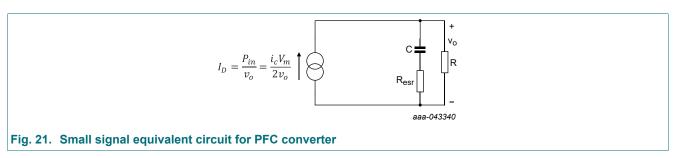

Fig. 21 shows the small signal equivalent circuit of PFC converter, C is the output capacitor, R<sub>esr</sub> is the series parasitic resistor, R is the load resistor.

Based on Fig. 21, the transfer function from  $V_c$  to  $v_o$  is given by

#### **Transition mode boost Power Factor Correction controller**

$$G_{iv}(s) = \frac{\widehat{v}_{o}(s)}{\widehat{v}_{c}(s)} = \frac{R}{2kk_{r}^{2}v_{o}^{2}R_{cs}} \frac{sR_{esr}C + 1}{s(3R_{esr} + R)C + 3} \approx \frac{R}{6kk_{r}^{2}v_{o}^{2}R_{cs}} \frac{1 + \frac{s}{\omega_{z}}}{1 + \frac{s}{\omega_{p}}}$$

(9)

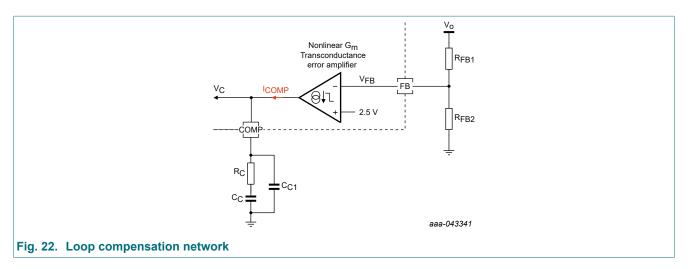

There are 1 pole  $\omega_z = \frac{1}{R_{esr}C}$  and 1 zero  $\omega_p = \frac{3}{RC}$  for PFC converter. Fig. 22 shows the compensation network for NEX83288. The loop control of NEX83288 is based on nonlinear transconductance error amplifier described in Section 13.3.5. Based on the compensation network, the control loop transfer function is given by

$$G_{vv}(s) = \frac{\widehat{v}_{c}(s)}{\widehat{v}_{o}(s)} = \frac{R_{FB2}G_{m}}{R_{FB1} + R_{FB2}} \frac{sR_{C}C_{C} + 1}{sC_{C}(sR_{C}C_{C1} + 1)} \quad (C_{C} > > C_{C1})$$

(10)

According to the above analysis, we can design the compensation parameters using k-factor method. The recommended compensation parameters under different load conditions are shown in <u>Table 11</u>.

**Table 11. Recommended compensation parameters**

| Maximum output power (W) | R <sub>C</sub> (kΩ) | C <sub>C</sub> (nF) | C <sub>C1</sub> (nF) |

|--------------------------|---------------------|---------------------|----------------------|

| 160                      | 51                  | 680                 | 100                  |

| 200                      | 68                  | 1000                | 220                  |

| 240                      | 33                  | 1000                | 220                  |

| 300                      | 22                  | 2200                | 220                  |

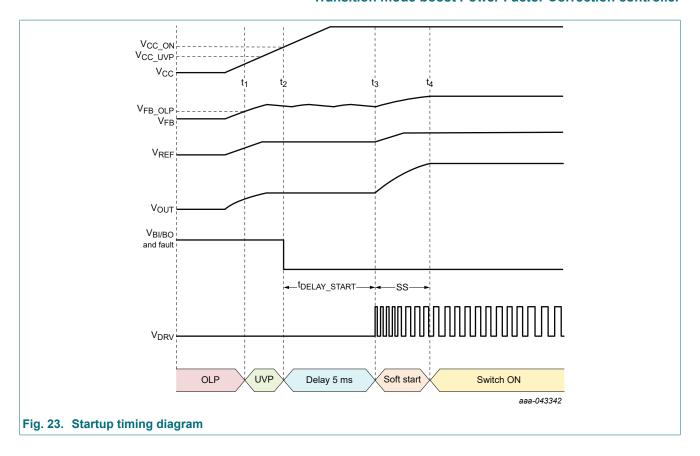

#### 13.3.3. Startup during normal operations

Fig. 23 shows the startup timing of NEX83288. The device is enabled when VCC is higher than the power on threshold  $V_{VCC\_ON}$  and disabled when VCC drops below the power-off (UVLO) threshold  $V_{VCC\_UVLO}$ .

Before VCC rises to  $V_{VCC\_ON}$ , the device is in a UVP or OLP state. After the device is powered on, it will check all the FAULT signals, including brown-in/brown-out and OLP protections. When  $V_{FB}$  is higher than the OLP threshold, the device will start a 5 ms delay and then enter the soft start state. During the soft start, the reference voltage rises from the current  $V_{FB}$  to 2.5 V and the output voltage slowly rises to the target voltage.

#### **Transition mode boost Power Factor Correction controller**

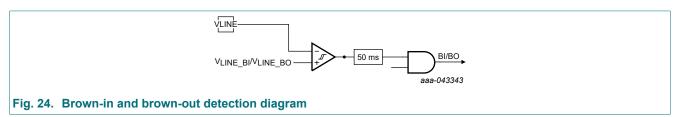

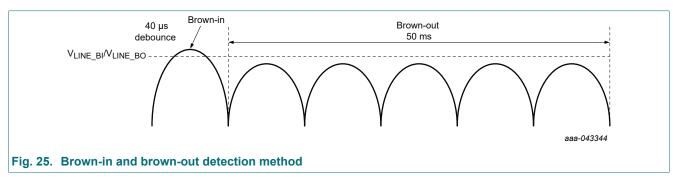

#### 13.3.4. Brown-in and brown-out

The VLINE pin of NEX83288 supports brown-in and brown-out detection. When the line voltage is continuously higher than the brown-in threshold  $V_{VLINE\ BI}$  for a debounce time, it is considered that the line voltage is normally connected.

When the line voltage drops continuously below the brown-out threshold  $V_{VLINE\_BO}$  for 50 ms, it is considered that the line voltage is abnormally connected. Fig. 24 and Fig. 25 show the brown-in/out detection diagram and method respectively.

#### **Transition mode boost Power Factor Correction controller**

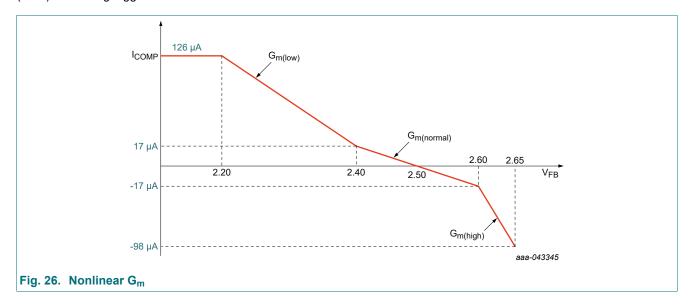

#### 13.3.5. Nonlinear transconductance error amplifier

To improve the dynamic of PFC converter, the device integrates a nonlinear transconductance error amplifier. Fig. 26 shows the nonlinear transconductance error amplifier output current varies with the feedback voltage. When the feedback voltage is lower than 2.1 V, the output current of error amplifier is clamped at 70  $\mu$ A.

- When the feedback voltage is between 2.1 V and 2.4 V, the equivalent transconduction is 300 μA/V.

- When the feedback voltage is between 2.4 V and 2.6 V, the equivalent transconduction is 100 μA/V.

- The equivalent transconduction will increase to 800 μA/V while the feedback voltage is higher than 2.6 V.

The output current of error amplifier changes according to the feedback voltage, which will charge and discharge the compensation network quickly. This ensures that COMP voltage is quickly pulled down to prevent over-voltage protection (OVP) from being triggered.

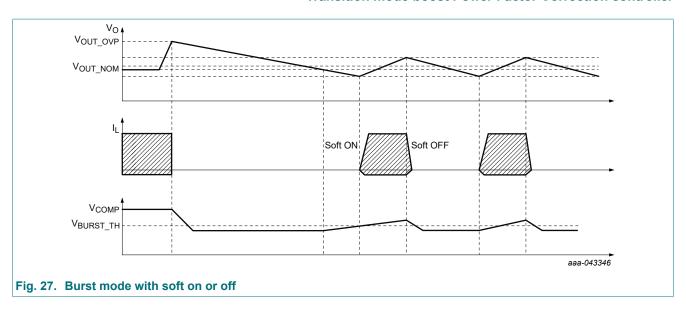

#### 13.3.6. Burst mode with soft on or off

Fig. 27 shows the burst mode control diagram.

- When the output voltage is higher than the OVP threshold, the device will shut down the PWM signal until the OVP signal is released. The burst mode is implemented based on the control voltage V<sub>COMP</sub>.

- When the control voltage V<sub>COMP</sub> is lower than the burst mode threshold, the device will shut down the PWM signal with five soft-OFF pulses.

- When the control voltage V<sub>COMP</sub> is higher than the burst mode threshold, the device will release the PWM signal with five soft-ON pulses.

This soft-ON/OFF control avoids abrupt inductor current changes and attenuates the acoustic noise accordingly. During the burst-off period, the device shuts down most of the internal block and ensures that the supply current is below  $I_Q$  (typically 460  $\mu$ A).

#### **Transition mode boost Power Factor Correction controller**

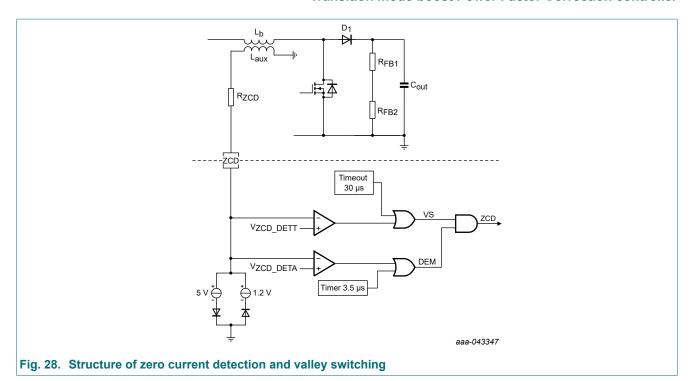

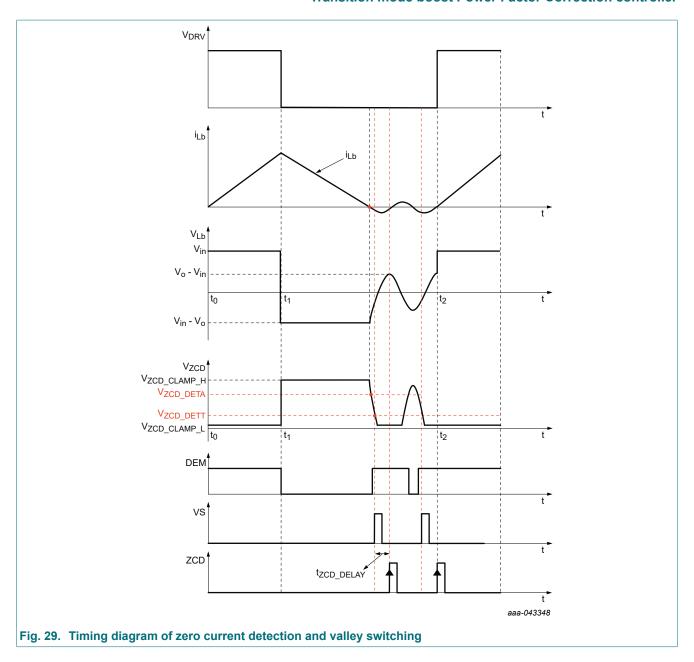

### 13.3.7. Zero current detection and valley switching

The zero current detection and valley switching is detected by the auxiliary winding and is implemented by ZCD pin. Fig. 28 shows the structure of zero current detection and valley switching.

The voltage of ZCD pin is upper and lower clamped at 5.7 V and 0.5 V respectively. There are two steps of threshold voltage for ZCD detection, one is for detecting the demagnetization point and the other is for detecting the valley point.

- When the ZCD voltage is lower than the demagnetization threshold voltage V<sub>ZCD\_DETA</sub>, it indicates the inductor current drops to zero.

- When the ZCD voltage is lower than the V<sub>ZCD DETT</sub>, it means that the MOSFET drain voltage drops to the valley region.

After a delay time  $t_{ZCD\_DELAY}$ , the ZCD signal is generated and the MOSFET is turned on at the valley point. Fig. 29 shows the timing diagram of zero current detection and valley switching. The external ZCD resistor is given by

$$R_{ZCD} \ge \frac{V_{L\_aux\_max} - V_{ZCD\_clamp}}{I_{ZCD\_DET}}$$

(11)

Where  $V_{L\_aux\_max}$  is the maximum voltage on the auxiliary winding,  $V_{ZCD\_clamp}$  is the upper clamp voltage on ZCD pin,  $I_{ZCD\_DET}$  is the maximum current on ZCD pin.

#### **Transition mode boost Power Factor Correction controller**

#### **Transition mode boost Power Factor Correction controller**

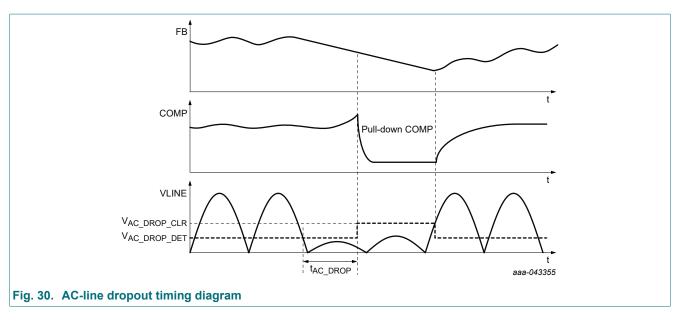

#### 13.3.8. AC-line drop detection

There is often the case that the AC-line voltage momentarily drops to zero or nearly zero, due to abnormal connection or transient abnormal events affecting the local AC-power distribution network.

During an AC-line dropout, the down-stream power stages depend on sufficient energy storage in the PFC output capacitance, which is sized to provide the ride-through energy for a specified hold-up time. Typically, while the PFC output voltage is falling, the voltage-loop error amplifier output will rise to maintain regulation.

Therefore, the excessive duty cycle is commanded when the AC-line voltage returns, and high peak current surges may saturate the boost inductor with possible overstress and audible noises.

#### **Transition mode boost Power Factor Correction controller**

NEX83288 supports an AC-line dropout detection function. When detecting the AC-line dropout event, the device will pull down the COMP voltage during the dropout and release the COMP voltage while the AC-line is resumed. If the VLINE voltage falls below  $V_{AC\_DROP\_DET}$  for longer than  $t_{AC\_DROP}$ , a dropout condition is detected, and the error amplifier output is turned off.

Besides, a pull-down current is applied to COMP to gently discharge the compensation network capacitors. In this way, when the AC-line voltage returns, the COMP voltage (and corresponding duty-cycle setting) remains very near to or even slightly below the level that it was before the dropout occurs. Current surges due to excessive duty-cycle, and their undesired attendant effects, are prevented.

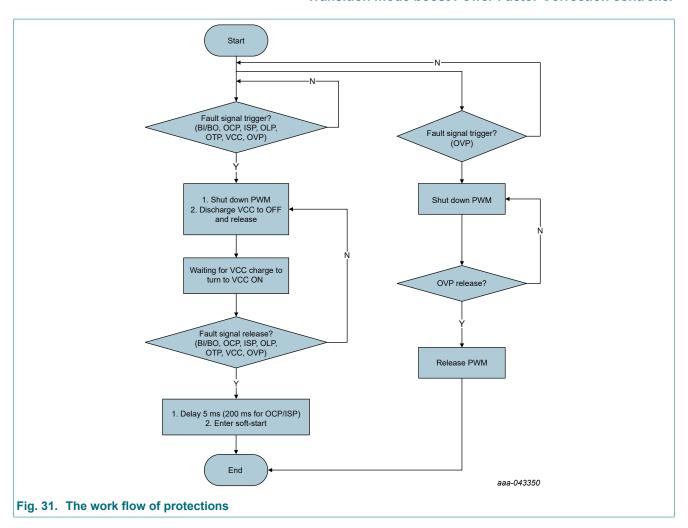

#### 13.3.9. Protections

Fig. 31 shows the protections action flowchart. The device supports brown-in/out, overcurrent protection (OCP), inductor saturation protection (ISP), open-loop protection (OLP), VCC overvoltage protection (VCC OVP) and overtemperature protection (OTP). There are three different actions for different protections:

- For brown-in/out, OLP, OTP, VCC OVP protections, when the fault signal is triggered, the device will shut down PWM output and then discharge VCC to V<sub>VCC\_OFF</sub> and release. If the fault signal does not release, the PWM remains off state and the VCC will charge and discharge between V<sub>VCC\_ON</sub> and V<sub>VCC\_OFF</sub>. When the fault signal is released, the device will enter soft start after 5 ms.

- 2. For ISP/OCP, when the fault signal is triggered, the action is the same as <u>1</u>. The only difference is the delay time from fault signal releases to soft start is increased to 200 ms.

- **3.** For OVP, when the fault signal is triggered, the device will shut down the PWM and wait for the OVP signal to release. If the OVP is released, the PWM will be released.

#### **Transition mode boost Power Factor Correction controller**

#### **Transition mode boost Power Factor Correction controller**

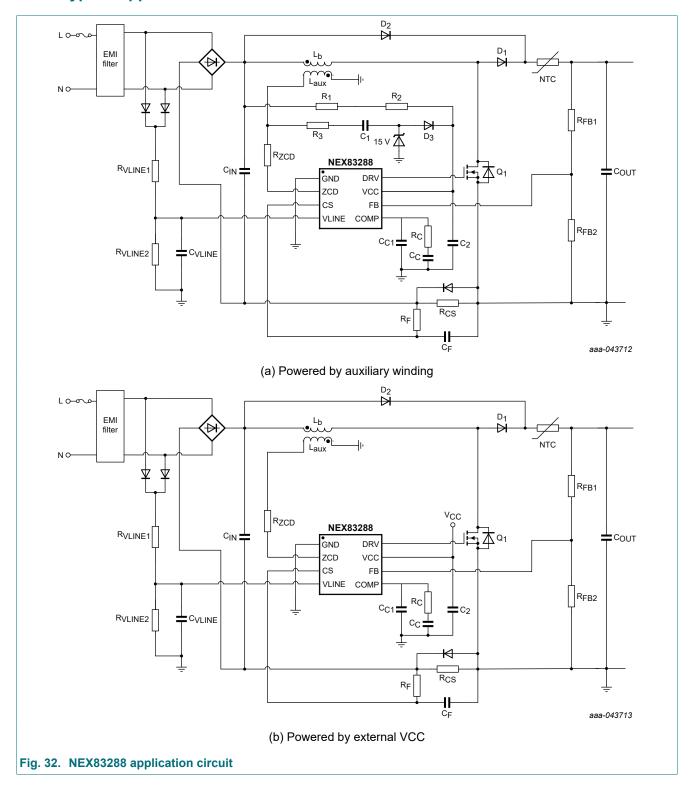

# 14. Application information

# 14.1. Typical application

#### **Transition mode boost Power Factor Correction controller**

### 14.2. Design requirements

Table 12 shows the specifications of a 240 W system.

**Table 12. System specifications**

| Symbol                 | Parameter            | Conditions                                     | Min | Тур  | Max | Unit     |  |

|------------------------|----------------------|------------------------------------------------|-----|------|-----|----------|--|

| Input characteristics  |                      |                                                |     |      |     |          |  |

| V <sub>AC(range)</sub> | AC voltage range     |                                                | 90  | -    | 264 | V        |  |

| f <sub>AC</sub>        | AC voltage frequency |                                                | 47  | -    | 63  | Hz       |  |

| V <sub>VCC_ON</sub>    | VCC on               |                                                | -   | 12   | -   | V        |  |

| V <sub>VCC_OFF</sub>   | VCC off              |                                                | -   | 9    | -   | V        |  |

| I <sub>IN</sub>        | input current        | input = 90 V <sub>ac</sub> ; full load = 240 W | -   | 2.78 | -   | Α        |  |

| Output characteristics |                      |                                                |     |      |     |          |  |

| V <sub>OUT</sub>       | output voltage       |                                                | -   | -    | 400 | V        |  |

| P <sub>L</sub>         | output power         |                                                | -   | -    | 240 | W        |  |

| V <sub>O(ripple)</sub> | output ripple        |                                                | -   | 12   | -   | $V_{pp}$ |  |

| System characteristics |                      |                                                |     |      |     |          |  |

| η <sub>peak</sub>      | peak efficiency      |                                                | -   | 96   | -   | %        |  |

### 14.3. Power stage design

#### 14.3.1. Rectifier bridge selection

The rectifier bridge is selected considering the maximum instantaneous voltage (the peak value of the line voltage) and the maximum input RMS current can be calculated by equation (12).

$$I_{AC\_MAX} = \frac{P_O}{\eta \times V_{AC\_MIN}} = 278 \quad A$$

(12)

The maximum peak input voltage is calculated by

$$V_{in\ max} = \sqrt{2} \times V_{AC\ MAX} = 373 \quad V \tag{13}$$

A standard 600 V/6 A rectifier bridge can be selected to provide enough margins.

#### 14.3.2. Input capacitor selection

The input capacitor behind the rectifier bridge is used to provide a bypass path for the high switching frequency current, and to suppress the ripple on the rectified sinusoidal input voltage.

Generally, 5% to 20% ripple on the input capacitor may be expected. Since the energy stored in the input capacitor is approximately equal to the energy transferred to the load in each switching cycle, equation (14) can be obtained:

$$\frac{1}{2}C_{in}\left(V_{AC\_MIN} + \frac{1}{2}rV_{AC\_MIN}\right)^2 - \frac{1}{2}C_{in}\left(V_{AC\_MIN} - \frac{1}{2}rV_{AC\_MIN}\right)^2 = \frac{P_0}{2\pi f_c}$$

(14)

where r is the ripple coefficient. Based on equation (14), the input capacitor can be calculated with equation (15):

$$C_{in} = \frac{P_O}{2\pi f_S \times r \times V_{AC\_MIN}^2} = \frac{I_{AC\_MAX}}{2\pi f_S \times r \times V_{AC\_MIN}}$$

(15)

Select a capacitor with good high-frequency performance, such as a film capacitor. Assume that the ripple coefficient is 0.1, the input capacitor can be calculated with equation (16):

NEX83288

All information provided in this document is subject to legal disclaimers.

© Nexperia B.V. 2025. All rights reserved

#### **Transition mode boost Power Factor Correction controller**

$$C_{in} = \frac{I_{AC\_MAX}}{2\pi f_s \times r \times V_{AC\_MIN}} = 0.49 \quad \mu F$$

(16)

Two 0.33 µF film capacitors with a 450 V voltage rating are recommended as the input capacitors because they provide high-frequency energy during the switching cycle.

#### 14.3.3. Boost inductor design

The boost inductor value is required to ensure that the maximum load can be delivered from the minimum input voltage, which can be calculated with equation (17):

$$L_{b\_max} \approx \frac{\eta \times V_{AC\_MIN}^2 \times 3.56}{2P_O} \times \frac{2 \times (1.5 + 0.75V_c - k_r V_m)}{\pi}$$

(17)

The unit of equation (17) is µH. Assume that V<sub>COMP</sub> is 3.2 V at full load, the inductor value is

$$L_{b\_max} \approx \frac{\eta \times V_{AC\_MIN}^2 \times 3.56}{2P_o} \times \frac{2 \times (1.5 + 0.75V_c - k_r V_m)}{\pi} = 111.41 \quad \mu H$$

(18)

The inductor value can be set as 110 µH.

#### 14.3.4. MOSFET selection

The current rating of MOSFET is determined by the maximum RMS value of the current following through the MOSFET. To calculate the RMS current of MOSFET in each half line cycle, we need to calculate the RMS current of MOSFET in each switching cycle first.

For TM mode, the RMS current of MOSFET in each switching cycle can be estimated with

$$I_{QRMS\_TM}(\theta) = \frac{i_{Lpk}(\theta)}{\sqrt{3}} \sqrt{\frac{T_{on}}{T_s}} = \frac{i_{Lpk}(\theta)}{\sqrt{3}} \sqrt{1 - \frac{v_{in}(\theta)}{v_{out}}}$$

(19)

Based on equation (19), the RMS value of MOSFET in each half line cycle can be calculated with

$$I_{QRMS\_TM} = \sqrt{\frac{1}{\pi}} \int_0^{\pi} \left[ \frac{i_{Lph}(\theta)}{\sqrt{3}} \sqrt{1 - \frac{v_{in}(\theta)}{v_{out}}} \right]^2 d\theta} = 2\sqrt{2} i_{in\_rms} \sqrt{\frac{1}{\pi}} \int_0^{\pi} \left( \frac{\sin(\theta)^2}{3} - \frac{\sqrt{2} v_{in\_rms} \sin(\theta)^3}{3v_{out}} \right) d\theta}$$

(20)

Simplify the formula to obtain equation (21)

$$I_{QRMS\_TM} = 2\sqrt{2} \, i_{in\_rms} \sqrt{\frac{1}{6} - \frac{4\sqrt{2} \, v_{in\_rms}}{9\pi v_{out}}}$$

(21)

The RMS current of MOSFET is

$$I_{QRMS\_TM} = 2\sqrt{2} \times I_{AC\_MAX} \sqrt{\frac{1}{6} - \frac{4\sqrt{2} \times V_{AC\_MIN}}{9\pi \times v_{out}}} = 2.74 A$$

(22)

Additionally, the MOSFET pulsed-drain current should exceed the peak inductor current, calculated with equation (23):

$$I_{O,Pulse} > 2\sqrt{2}I_{AC,MAX} = 7.86 A$$

(23)

**Nexperia**

#### **Transition mode boost Power Factor Correction controller**

#### 14.3.5. Boost diode selection

For TM mode, the average current of diode is equal to the output current. The RMS current of the diode is calculated with equation (24):

$$I_{DRMS\_TM} = \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \left[ \frac{i_{Lpk}(\theta)}{\sqrt{3}} \sqrt{\frac{v_{in}(\theta)}{v_{out}}} \right]^{2} d\theta = 2\sqrt{2} i_{in\_rms} \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{\sqrt{2} v_{in\_rms} \sin(\theta)^{3}}{3v_{out}} d\theta$$

(24)

Simplify the formula to obtain equation (25):

$$I_{DRMS\_TM} = 2\sqrt{2} i_{in\_rms} \sqrt{\frac{4\sqrt{2} v_{in\_rms}}{9\pi v_{out}}} = 1.67 A$$

(25)

The boost diode must have average and RMS current ratings that exceed IDAVG and IDRMS, respectively.

#### 14.3.6. Output capacitor selection

When selecting the output capacitor, we need to consider the following conditions: the output voltage ripple (VO PP), ripple current rating, and hold-up time. The output ripple is a function of the effective series resistance (ESR) of the output capacitor, the output voltage, and the line frequency (f<sub>1</sub>). Based on the energy balance, the energy on the output capacitor is

$$P_{c}(t) = v_{out}i_{c}(t) = P_{in}(t) - P_{o} = 2I_{in\_rms}V_{in\_rms}[\sin(\omega_{L}t)]^{2} - P_{o} = 2P_{o}[\sin(\omega_{L}t)]^{2} - P_{o}$$

(26)

Based on equation (26), the current following to the output capacitor is calculated by

$$i_c(t) = 2I_o[\sin(\omega_L t)]^2 - I_o = -I_o \cos(2\omega_L t)$$

(27)

Considering the ESR of output capacitor, the output ripple is calculated by

$$V_{o\_pp} = 2 \times \frac{P_o}{v_{out}} \times \sqrt{R_{esr}^2 + \frac{1}{(2 \times 2\pi f_L \times C_o)^2}}$$

(28)

In this case, the calculated ripple with the selected capacitor should be below 3% of the output voltage, and the ESR of the output capacitor is assumed to be 1  $\Omega$ .  $C_{\Omega}$  can be calculated by

$$C_o \ge \frac{1}{2 \times 2\pi f_L \sqrt{\left(\frac{3\% \times v_{out}^2}{2 \times P_o}\right)^2 - R_{esr}^2}} = 160 \ \mu F$$

(29)

In this example design, an aluminum electrolytic capacitor with specification of 180 µF/450 V is recommended.

For TM mode, the maximum RMS ripple current flowing in the output capacitor can be estimated with equation (30).

$$I_{o\_ripple\_max} = \sqrt{I_{DRMS\_TM}}^2 - \left(\frac{P_o}{v_{out}}\right)^2 = 1.56 \quad A$$

(30)

This current flowing into the output capacitor is made up of a double line frequency ripple component (2 x f<sub>1</sub>) and a switching frequency component (f<sub>sw</sub>), calculated with equation (31) and equation (32), respectively.

$$I_{o\_ripple\_100Hz} = \frac{P_o}{\sqrt{2}v_{out}} = 0.424 A$$

(31)

$$I_{o\_ripple\_100Hz} = \frac{P_o}{\sqrt{2}v_{out}} = 0.424 \quad A$$

$$I_{o\_ripple\_fsw} = \sqrt{I_{o\_ripple\_max}^2 - I_{o\_ripple\_100Hz}^2} = 1.501 \quad A$$

(31)

The capacitor should be chosen so that the hold-up time satisfies the relationship calculated with equation (33):

All information provided in this document is subject to legal disclaimers

#### **Transition mode boost Power Factor Correction controller**

$$C_o = \frac{2 \times P_o \times t_{hold}}{\eta \times (v_{out}^2 - v_{out\_hold}^2)}$$

(33)

Where V<sub>OUT</sub> is the minimum output voltage under normal operating conditions, and v<sub>OUT\_hold</sub> is the required minimum operating output voltage to supply the second stage DC-DC converter when the line voltage is shut down.

### 14.4. Control circuit design

#### 14.4.1. FB section

The internal reference voltage  $V_{REF}$  is 2.5 V (typical), based on the internal reference voltage, the resistor division ratio is calculated with

$$\frac{R_{FBDWN}}{R_{FBUP} + R_{FBDWN}} \times V_{out} = V_{REF}$$

(34)

Since the division resistor will affect the standby power, the selection of resistance value needs to consider standby power consumption. It is recommended that the upper resistor is set as 6.6 m $\Omega$ . Based on equation (34), the lower resistor can be calculated with

$$R_{FBDWN} = \frac{V_{REF}}{v_{out} - V_{REF}} \times R_{FBUP}$$

(35)

#### 14.4.2. VLINE section

Considering the brown-in and brown-out threshold, the resistors on VLINE pin can be calculated with equation (36).

$$\frac{R_{LDWN}}{R_{LUP} + R_{LDWN}} \times V_{in\_pk} = V_{BRI} \tag{36}$$

Since the division resistors also affect the standby power, the selection of resistance value needs to consider standby power consumption. It is recommended that the upper resistor is set as 6.6 m $\Omega$ . Based on equation (37), the lower resistor can be calculated with

$$R_{LDWN} = \frac{V_{BRI}}{V_{in\ pk} - V_{BRI}} \times R_{LUP} \tag{37}$$

#### 14.4.3. ZCD section

The external ZCD resistor is given by

$$R_{ZCD} \ge \frac{V_{L\_aux\_max} - V_{ZCD\_clamp}}{I_{ZCD\_DET}}$$

(38)

Where  $V_{L\_aux\_max}$  is the maximum voltage on the auxiliary winding,  $V_{ZCD\_clamp}$  is the upper clamp voltage on ZCD pin,  $I_{ZCD\_DET}$  is the maximum current on ZCD pin.

#### 14.4.4. CS section

CS is used for CBC and control. The current flowing through the MOSFET should be below the CBC threshold. The CS resistor value can be estimated with equation (39):

$$R_{CS} \le \frac{V_{CBC}}{2\sqrt{2} \times I_{AC\ MAX}} \tag{39}$$

#### **Transition mode boost Power Factor Correction controller**

In this case, the calculated CS resistor is 63.6 m $\Omega$ , the resistor can be selected as 50 m $\Omega$ . To suppress the spike and improve the control reliability, a low pass filter (220  $\Omega$  + 220 pF) is recommended to be added on CS.

#### 14.4.5. COMP section

The compensation parameters can be calculated by the k-factor method. The k-factor method design steps are as follows:

1. For maximum phase Boost at the gain cross-over frequency, compensator design proceeds by placing the pole and zero an equal distance above and below the gain cross-over frequency  $(f_c)$  on the bode plot. That is

$$\begin{cases} f_{z1} = \frac{f_c}{k} \\ f_{p1} = f_c \times k \end{cases} \tag{40}$$

2. The system phase at the gain cross-over frequency is given by

$$\emptyset_{PS} = arctan\left(\frac{f_c}{f_z}\right) - arctan\left(\frac{f_c}{f_p}\right)$$

(41)

Based on equation (40) and (41), the open loop transfer function is

$$G_{iv}(s)G_{vv}(s) = \frac{R}{6kk_r^2 v_o^2 R_{CS}} \frac{R_{FB2}G_m}{R_{FB1} + R_{FB2}} \frac{1 + \frac{s}{\omega_Z}}{1 + \frac{s}{\omega_P}} \frac{1 + \frac{s}{\omega_{Z1}}}{sC_C(1 + \frac{s}{\omega_{P1}})}$$

(42)

Where  $\omega_{z1}$  =  $2\pi f_{z1}$  =  $\frac{1}{R_C C_C}$  and  $\omega_{p1}$  =  $2\pi f_{p1}$  =  $\frac{1}{R_C C_{C1}}$ .

The compensator expected phase boost of the compensator is given by

$$\emptyset_{boost} = \emptyset_{PM} - \emptyset_{PS} - \frac{\pi}{2} = arc \tan\left(\frac{f_c}{f_{z1}}\right) - arc \tan\left(\frac{f_c}{f_{p1}}\right) = arc \tan\left(k\right) - arc \tan\left(\frac{1}{k}\right)$$

(43)

Furthermore, since  $arctan(k) + arctan(\frac{1}{k}) = \frac{\pi}{2}$ , k can be derived from equation (44)

$$k = \tan\left(\frac{\phi_{PM} - \phi_{PS}}{2}\right) \tag{44}$$

3.  $R_C$ ,  $C_C$  and  $C_{C1}$  are calculated by the system gain at cross over frequency:

$$C_{C} = \frac{R}{6kk_{r}^{2}v_{o}^{2}R_{CS}} \frac{R_{FB2}G_{m}}{R_{FB1} + R_{FB2}} \frac{k}{2\pi f_{c}} \sqrt{\frac{1 + \left(\frac{f_{c}}{f_{z}}\right)^{2}}{1 + \left(\frac{f_{c}}{f_{p}}\right)^{2}}}$$

$$R_{C} = \frac{k}{2\pi f_{c}C_{C}}$$

$$C_{C1} = \frac{1}{2\pi k f_{c}R_{C}}$$

(45)

Select the appropriate gain cross-over frequency  $f_{\rm C}$  (< 20 Hz) and phase margin  $\phi_{PM}$  ( $\geq$  65 °C), the compensator parameters can be calculated by equation (45). In this case, the recommended compensation parameters are  $C_{\rm C}$  = 1  $\mu$ F,  $R_{\rm C}$  = 33 k $\Omega$ ,  $C_{\rm C1}$  = 220 nF.

#### **Transition mode boost Power Factor Correction controller**

# 15. Package outline

Fig. 33. Package outline SOT96-2 (SO8)

#### **Transition mode boost Power Factor Correction controller**

# 16. Abbreviations

#### **Table 13. Abbreviations**

| Acronym | Description                                       |

|---------|---------------------------------------------------|

| AC      | Alternating Current                               |

| ACM     | Average Current Mode                              |

| ANSI    | American National Standards Institute             |

| BI      | Brown-in                                          |

| ВО      | Brown-out                                         |

| ССМ     | Continuous Conduction Mode                        |

| CDM     | Charged Device Model                              |

| CrM     | Critical Conduction Mode                          |

| COT     | Constant On Time                                  |

| DC      | Direct Current                                    |

| DCM     | Discontinuous Conduction Mode                     |

| EMI     | ElectroMagnetic Interference                      |

| ESD     | ElectroStatic Discharge                           |

| ESDA    | ElectroStatic Discharge Association               |

| GaN     | Gallium Nitride                                   |

| НВМ     | Human Body Model                                  |

| HEMT    | High Electron Mobility Transistor                 |

| IC      | Integrated Circuit                                |

| ISP     | Inductor Saturation Protection                    |

| JEDEC   | Joint Electron Device Engineering Council         |

| LCD     | Liquid Crystal Display                            |

| MOSFET  | Metal-Oxide-Semiconductor Field-Effect Transistor |

| OCP     | OverCurrent Protection                            |

| OLP     | Open Loop Protection                              |

| OPP     | OverPower Protection                              |

| OTP     | OverTemperature Protection                        |

| OVP     | OverVoltage Protection                            |

| PFC     | Power Factor Correction                           |

| PWM     | Pulse-Width Modulation                            |

| THD     | Total Harmonic Distortion                         |

| TM      | Transition Mode                                   |

| UVLO    | Under-Voltage LockOut                             |

| UVP     | UnderVoltage Protection                           |

| VOT     | Variable On Time                                  |

#### **Transition mode boost Power Factor Correction controller**

# 17. Revision history

#### Table 14. Revision history

| Table 1 in Novicion inicitory |                                                                                                                                                                             |                    |               |               |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------|---------------|

| Document ID                   | Release date                                                                                                                                                                | Data sheet status  | Change notice | Supersedes    |

| NEX83288 v. 1.1               | 20250916                                                                                                                                                                    | Product data sheet | -             | NEX83288 v. 1 |

| Modifications:                | <ul> <li>Fig. 18: Functional block diagram updated.</li> <li>Table 12: The symbol of peak efficiency updated.</li> <li>Fig. 33: Package outline drawing updated.</li> </ul> |                    |               |               |

| NEX83288 v. 1                 | 20250821                                                                                                                                                                    | Product data sheet | -             | -             |

#### **Transition mode boost Power Factor Correction controller**

## 18. Legal information

#### **Data sheet status**

| Document status [1][2]         | Product<br>status [3] | Definition                                                                            |

|--------------------------------|-----------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development           | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification         | This document contains data from the preliminary specification.                       |

| Product [short]<br>data sheet  | Production            | This document contains the product specification.                                     |

- Please consult the most recently issued document before initiating or completing a design.

- 2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the internet at <a href="https://www.nexperia.com">https://www.nexperia.com</a>.

#### **Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

Right to make changes — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal

injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — Nexperia products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nexperia.com/profile/terms">http://www.nexperia.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of Nexperia products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific Nexperia product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. Nexperia accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without Nexperia's warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond Nexperia's specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies Nexperia for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond Nexperia's standard warranty and Nexperia's product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### **Trademarks**

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

NEX83288

All information provided in this document is subject to legal disclaimers.

© Nexperia B.V. 2025. All rights reserved

#### **Transition mode boost Power Factor Correction controller**

# **Contents**

| 1. General description                              |     |

|-----------------------------------------------------|-----|

| 2. Features and benefits                            |     |

| 3. Applications                                     |     |

| 4. Ordering information                             |     |

| 5. Marking                                          | . 2 |

| 6. Pin configuration and description                | . 2 |

| 6.1. Pin configuration                              | 2   |

| 6.2. Pin description                                |     |

| 7. Limiting values                                  | . 3 |

| 8. ESD ratings                                      | . 3 |

| 9. Recommended operating conditions                 | 3   |

| 10. Thermal characteristics                         | . 3 |

| 11. Electrical characteristics                      | 4   |

| 12. Typical characteristics                         |     |

| 13. Detailed Description                            |     |

| 13.1. Overview                                      | 10  |

| 13.2. Functional block diagram                      | 10  |

| 13.3. Feature description                           | 11  |

| 13.3.1. ACM-based On time control                   | 11  |

| 13.3.2. Loop compensation                           | 13  |

| 13.3.3. Startup during normal operations            | 14  |

| 13.3.4. Brown-in and brown-out                      | 15  |

| 13.3.5. Nonlinear transconductance error amplifier  | 16  |

| 13.3.6. Burst mode with soft on or off              | 16  |

| 13.3.7. Zero current detection and valley switching | 17  |

| 13.3.8. AC-line drop detection                      | 19  |

| 13.3.9. Protections                                 | 20  |

| 14. Application information                         | 22  |

| 14.1. Typical application                           | 22  |

| 14.2. Design requirements                           | 23  |

| 14.3. Power stage design                            | 23  |

| 14.3.1. Rectifier bridge selection                  | 23  |

| 14.3.2. Input capacitor selection                   | 23  |

| 14.3.3. Boost inductor design                       | 24  |

| 14.3.4. MOSFET selection                            | 24  |

| 14.3.5. Boost diode selection                       | 25  |

| 14.3.6. Output capacitor selection                  | 25  |

| 14.4. Control circuit design                        | 26  |

| 14.4.1. FB section                                  | 26  |

| 14.4.2. VLINE section                               | 26  |

| 14.4.3. ZCD section                                 | 26  |

| 14.4.4. CS section                                  | 26  |

| 14.4.5. COMP section                                | 27  |

| 15. Package outline                                 | 28  |

| 16. | Abbreviations     | 29 |

|-----|-------------------|----|

| 17. | Revision history  | 30 |

| 18. | Legal information | 31 |

#### <sup>©</sup> Nexperia B.V. 2025. All rights reserved

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 16 September 2025